Table of Contents

Trigger

The main purpose of the trigger is to implement a coincidence between the S800 focal-plane fast timing scintillator E1 and a secondary detector generally located at the target location. This coincidence is often a mandatory requirement when the trigger rate of the S800 alone (S800 singles) is too high for the data acquisition and the resulting dead time is prohibitive.

The trigger logic is implemented in a LeCroy 2367 Universal Logic Module (ULM) by means of its XC4000E Xilinx FPGA. The main motivations for implementing the trigger logic in an FPGA driven module are the following:

- Simplify cabling and setup of the trigger

- Reduce the number of modules used to implement the trigger

- Ability to remotely control and inspect trigger signals

- Ability to save and restore the trigger configuration

- Direct visualization of the trigger logic and configuration

Probably the most appealing feature of this module is the possibility to remotely control the trigger timing and configuration while beam is present in the vault, since most experiments are nowadays locating their electronics close to the detectors. For more details on this detector check section “Trigger module”.

The S800 trigger from the E1 scintillator provides also the reference time for the CRDCs as well as time-of-flight measurements. Note that because the FPGA uses a 40 MHz internal clock, the time reference of the signals in the trigger circuit set the phase of that clock, and therefore jitter by 25 ns with respect to the source signals. This jitter is measured with a TDC and can be subtracted to the time measurements to recover the timing relative to the source signals.

Trigger schematics

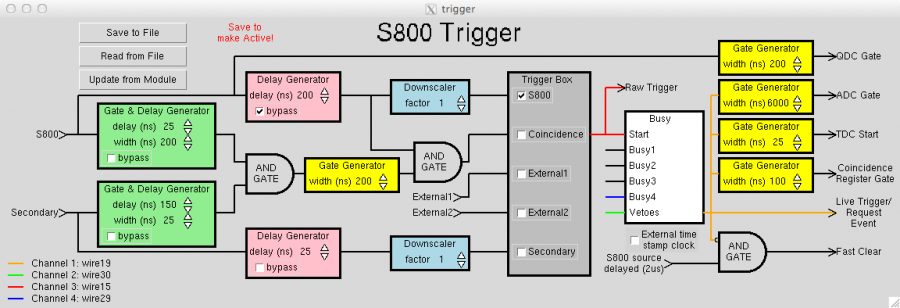

The trigger schematic is shown on the Graphical User Interface (GUI) displayed in the figure below. The GUI is automatically displayed when clicking in the Readout icon of the u4pc8 desktop.

The two main trigger sources are labeled “S800” and “Secondary” in the GUI (the leftmost side of the layout). Each source is routed to a gate and delay generator before forming a coincidence in the following AND gate. The AND signal is then widened before being ANDed with the delayed S800 source signal. The purpose of the second AND gate is to reset the timing of the coincidence to the S800 timing. This is necessary in case the secondary detector has a slow timing and large jitter (Germanium detectors for instance). Single triggers from each trigger source are also available in a second branch, after going through a delay generator followed by a downscaler (used to take a reduced number of events from the trigger sources). Note that each gate and delay generator can be bypassed.

Trigger box

In addition to the singles and coincidence triggers, two separate trigger sources labeled “External 1” and “External 2” can be used. The various sources can be selected from the trigger box to define the raw trigger, which is then sent to a third AND gate for computer busy rejection. The busy latch (on the middle) is set by the raw trigger after a 50 ns delay, and prevents subsequent events to be accepted. It is reset by the computer once the current event has been processed. The live trigger signal feeds several gate generators which provide appropriate gates for the ADCs, QDCs, TDCs and an eventual coincidence register. Note that the trigger box contains its own coincidence register for which the input signals are delayed by 50 ns, and the gate width is set by the coincidence gate generator. The request event signal is latched before being sent to the computer.

Since more than one trigger source can be selected, it is possible that more than one pulse is generated at the output of the trigger box, depending on the timing and shape of the source signals. When both downscaled singles and coincidences are selected for instance, the “Raw trigger” output of the trigger box may generate two pulses for a single event. A scaler connected to the “Raw trigger” output will therefore not reflect the true number of events. For this reason scalers are also connected to individual inputs of the trigger box (for more details, check the section “Scalers and dead time”). A trigger register word (bit pattern) is written at each occurrence of a live trigger signal. This word is the first being read out from the trigger module, prior to the time stamp (check trigger packet tag 0x2367 in the DAQ section for more information).

More details about the trigger box module and its FPGA schematics can be found in section “Trigger module”.

Gate generation

All digitizer gates and start signals are derived from the live trigger signal, with the exception of the QDC gate which is directly generated from the S800 source signal. The reason is to avoid long analog delays on the scintillator signals. A fast clear circuit is provided to clear the QDC if no valid trigger was generated.

Inspect channels

A set of four inspect channels are patched out to the data-U4 panels. Each channel can be assigned to any connection drawn on the GUI by right clicking on the corresponding drawn “wire”, thereby providing a convenient way to diagnose and adjust the timings at each step of the trigger circuit.

Busy Circuit

As each controller and external data acquisition perform their readout sequence in parallel, they have different busy times. The busy circuit following the generation of raw triggers is mainly composed of a latch that is set by the “Raw trigger” signal, and cleared by the falling edge of the OR of the individual busy signals (Busy inputs) coming from individual crate controllers or other data acquisition systems. This way the “Live trigger” signal stays true as long as the longest busy signal. The “Live trigger” signal is therefore a “global busy” signal as well. In addition, the same busy signals of individual crate controllers or other data acquisition system are used to veto the “Raw trigger” signal and prevent the generation of a live trigger. This takes care of situations where separate triggers are generated for some of the crate controllers or other data acquisition systems (such as scaler readout sequences), during which no event readout sequence should be started.

Time Stamping Scheme

Because the USB-based S800 data acquisition uses independent crate controllers that perform the readout in parallel, time stamping schemes are incorporated in the trigger to synchronize events. Because of this modularity, the same synchronization scheme can be used when coupling external data acquisition systems to the S800.

More details about the time stamping module can be found in section “Time stamping”.

Trigger module

The S800 trigger logic is built in a FPGA LeCroy 2367 Universal Logic Module (ULM). Note that this module could be replaced in the future by another FPGA module provided it has enough NIM or ECL input/outputs (such as the VME XLM72 module for instance). This section contains the functionality of the S800 trigger module and the commands used to control its parameters.

CAMAC commands

A table with the list of the CAMAC commands recognized by the trigger module and their signification can be found here.

Inputs and outputs

The list of inputs/outputs channels to/from the ULM trigger module, and their assignment, is shown in the bale below:

| Pin | Assignment | Pin | Assignment | Pin | Assignment | Pin | Assignment |

|---|---|---|---|---|---|---|---|

| A1 (in) | S800 source | B1 (out) | Raw trigger | C1 (in) | Busy 1 | D1 (out) | S800 source |

| A2 (in) | Secondary source | B2 (out) | Live trigger | C2 (in) | Busy 2 | D2 (out) | Secondary source |

| A3 (in) | External 1 source | B3 (out) | ADC gate | C3 (in) | Busy 3 | D3 (out) | External 1 source |

| A4 (in) | External 2 source | B4 (out) | QDC gate | C4 (in) | Busy 4 | D4 (out) | External 2 source |

| A5 (in) | Clear busy | B5 (out) | TDC start | C5 (in) | Busy 5 | D5 (out) | S800 trigger |

| A6 (in) | Clear module | B6 (out) | Trigger register gate | C6 (in) | Busy 6 | D6 (out) | Coincidence trigger |

| A7 (in) | Gretina sync | B7 (out) | C7 (in) | Busy 7 | D7 (out) | External 1 trigger | |

| A8 (in) | Time stamp clock | B8 (out) | Live trigger | C8 (in) | Time stamp latch | D8 (out) | External 2 trigger |

| B9 (out) | Inspect 1 | C9 (out) | Time stamp clock | D9 (out) | Secondary trigger | ||

| B10 (out) | Inspect 2 | C10 (out) | Time stamp latch | D10 (out) | Raw trigger | ||

| B11 (out) | Inspect 3 | C11 (out) | D11 (out) | Live trigger | |||

| B12 (out) | Inspect 4 | C12 (out) | D12 (out) | Raw pulser | |||

| B13 (out) | Fast clear | C13 (out) | D13 (out) | Live pulser | |||

| B14 (out) | C14 (out) | D14 (out) | Fast clear | ||||

| B15 (out) | Go | C15 (out) | D15 (out) | 10 Hz | |||

| B16 (out) | Time stamp clock | C16 (out) | D16 (out) | 1 Hz |

FPGA firmware

The firmware of the trigger module is shown in the following files. The PDF file contains the schematic sheets, used for most of the design. The Verilog file contains the block dealing with CAMAC communications.

Time stamping

The S800 ULM trigger module provides a vetoed 10 MHz clock signal (derived from the 40 MHz FPGA clock) used for time stamping. An external clock can also be used (as it is done, for instance, when running with GRETINA). The clock is inhibited by a “Go” signal controlled by the trigger module. While “Go” is false, all time stamp counters can be reset via CAMAC command, typically during the begin sequences of the controllers or data acquisitions (see section “Begin sequence”). The clock signal is released when the “Go” signal is set to true at the end of the begin sequence. This simple scheme insures that all time stamp counters are synchronized.

The time stamping clock is available as an output that can be distributed to other time stamp modules, such as the one located in the S800 VME crate (or in other data acquisition systems coupled to the S800). The S800 VME time-stamp module is implemented in a XLM72 (SpartanXL) FPGA. The schematics of the firmware is available here. The inputs are the following:

E1: time stamp clock input

E2: latch input

E3: clear input

The clear can be done via software as well, and is usually done that way.

The Verilog file contains the code of the REGISTERS module of the FPGA configuration, responsible for the communication with the VME.

Configuration for S800 in tandem with other detectors

In its standard configuration, the S800 data acquisition uses one CAMAC crate and one VME crate only. The CC-USB and VM-USB crate controller modules performing the readout are connected to the latches number 1 and 2 (inputs C1 and C2) of the trigger module, respectively. Each crate controller is configured to output their busy and end-of-event signals on their available NIM outputs, which are then connected to the appropriate inputs on the trigger module. To incorporate an external detector in the S800 trigger logic, the same busy and end-of-event signals are required from its data acquisition system. This is to ensure that no live trigger signal is generated when any of the partners is busy or still processing an event. The 5 signals necessary between the S800 trigger and an external data acquisition system are the following:

- Raw trigger from external detector to Secondary source

- Live trigger from S800 trigger to external data acquisition (trigger input)

- Time stamp clock from S800 trigger to external data acquisition (time stamp input)

- End-of-event from external data acquisition to S800 trigger

- Busy from external data acquisition to S800 trigger

Begin sequence

OBSOLETE: THIS SECTION IS BEING UPDATED

The internal “Go” state of the trigger module is controlled via CAMAC commands. When “Go” is false, the trigger and time stamp clock signals are vetoed and therefore absent. This way all time stamp counters can be safely zeroed during the beginning sequence of the data acquisition systems. The last command of the CAMAC beginning sequence sets the “Go” state to true, at which point both trigger and time stamp signals are released. This mechanism ensures that all time stamp counters are synchronized.

The data acquisition begin sequence of the trigger module is the following:

- reset time stamp counter to 0

- reset trigger register to 0

- after all modules in all crates have been initialized, send CAMAC command to set “Go” state to true

- after a preset delay of 200 to 300 microseconds, the “Go” level is set to true

The last step of the begin sequence allows enough time for the CC-USB crate controller to switch from its interactive mode to data acquisition mode. The end sequence script executed at the end of a run sets the “Go” state of the module back to false.

Scalers and dead time

The “D” connector of the trigger module is directly connected to first 16 inputs of a 32-channel scaler LeCroy 4434 module (see mapping of the inputs and outputs of the trigger module in section Inputs and outputs). Scalers are connected to each of the trigger source inputs, as well as trigger box inputs. These scalers can be used to recover the number of trigger signals occurring on each of the source and trigger box inputs, besides the information coded for each event in the trigger register.

For the determination of the dead time, both a free running and vetoed 10 kHz pulser signal are also connected to scalers. This is the preferred method because the pulser is not subject to possible double triggering effects like the raw trigger.

The remining 16 scaler input channels (pins 17 to 32 in module) are connected to an ECL-NIM-ECL converter fed by a 16-channel Mesytec CFD (MCFD-16), which sends the signals from the S800 detectors (E1 up, E1 down, CRDC1, CRDC2, OBJ_SCI, A1900 SCI, and OR Hodoscope).

The complete list of scaler channels can be found here.